Core 2 CPU 電源状態の調査中 ("C 状態 ")、私は実際にレガシー Intel Core/Core 2 プロセッサのほとんどのサポートを実装することができました。すべての背景情報を含む完全な実装 (Linux パッチ) は、ここに文書化されています。

これらのプロセッサに関する情報をさらに蓄積するにつれて、Core 2 モデルでサポートされている C ステートは、以前のプロセッサと後のプロセッサの両方よりもはるかに複雑であることが明らかになり始めました。これらは、拡張 C ステートとして知られています。 (または「CxE これには、パッケージ、個々のコア、およびチップセット上のその他のコンポーネント (メモリなど) が含まれます。その時点で 07 ドライバーがリリースされましたが、コードは特に成熟しておらず、競合する C ステート サポートを持ついくつかの Core 2 プロセッサがリリースされました。

Core 2 Solo/Duo C-state サポートに関する説得力のある情報が、2006 年のこの記事で見つかりました。これは Windows でのサポートに関連していますが、これらのプロセッサでの堅牢なハードウェア C-state サポートを示しています。 Kentsfield に関する情報は実際のモデル番号と矛盾しているため、実際には以下の Yorkfield について言及していると思われます:

<ブロック引用>...クアッドコア Intel Core 2 Extreme (Kentsfield) プロセッサは、5 つのパフォーマンスおよび省電力テクノロジすべてをサポートします — 強化された IntelSpeedStep (EIST)、サーマル モニター 1 (TM1) およびサーマル モニター 2 (TM2)、古いオンデマンド クロック変調 ( ODCM)、および拡張 C ステート (CxE)。拡張停止 (C1) 状態のみを特徴とする Intel Pentium 4 および Pentium D 600、800、および 900 プロセッサと比較して、この機能は Intel Core 2 プロセッサ (および Intel Core Solo/Duo プロセッサ) で可能なすべてのStop Grant (C2)、Deep Sleep (C3)、DeeperSleep (C4) など、プロセッサのアイドル状態。

2008 年のこの記事では、Core 2 Duo および Core 2 Quad を含むマルチコア Intel プロセッサでのコアごとの C ステートのサポートについて概説しています (追加の役立つ背景情報は、Dell のこのホワイト ペーパーに記載されています)。

<ブロック引用>コア C ステートは、ハードウェア C ステートです。いくつかのコアのアイドル状態があります。 CC1 と CC3。ご存知のように、最近リリースされた Core DuoT5000/T7000 モバイル プロセッサ (一部のサークルでは Penryn として知られています) など、最新のプロセッサには複数のコアがあります。私たちがCPU /プロセッサと考えていたものは、実際には複数の汎用CPUがその中にあります。 Intel Core Duo には、プロセッサ チップに 2 つのコアがあります。 Intel Core-2 Quad には、プロセッサ チップごとに 4 つのコアがあります。これらの各コアには、独自のアイドル状態があります。これは、1 つのコアがアイドル状態で、別のコアがスレッドで懸命に作業している可能性があるため、理にかなっています。したがって、コア C ステートは、これらのコアの 1 つのアイドル状態です。

12 に関する追加の背景を提供するインテルの 2010 年のプレゼンテーションを見つけました。 ドライバーですが、残念ながら Core 2 のサポートの欠如については説明していません:

この実験的ドライバーは、Intel AtomProcessor、Intel Core i3/i5/i7 プロセッサー、および関連する Intel Xeon プロセッサーの acpi_idle に取って代わります。 Intel Core2 プロセッサ以前には対応していません。

上記のプレゼンテーションは、 27 が ドライバーは、Linux カーネル構成に影響を与える「メニュー」CPU ガバナーの実装です (つまり、39 対 42 )。はしごガバナーとメニュー ガバナーの違いは、この回答で簡潔に説明されています。

Dell には、C-state C0 から C6 への互換性をリストした役立つ記事があります。

<ブロック引用>モード C1 ~ C3 は基本的に CPU 内部で使用するクロック信号をカットすることで動作し、モード C4 ~ C6 は CPU の電圧を下げることで動作します。 「拡張」モードでは、両方を同時に実行できます。

Mode Name CPUs

C0 Operating State All CPUs

C1 Halt 486DX4 and above

C1E Enhanced Halt All socket LGA775 CPUs

C1E — Turion 64, 65-nm Athlon X2 and Phenom CPUs

C2 Stop Grant 486DX4 and above

C2 Stop Clock Only 486DX4, Pentium, Pentium MMX, K5, K6, K6-2, K6-III

C2E Extended Stop Grant Core 2 Duo and above (Intel only)

C3 Sleep Pentium II, Athlon and above, but not on Core 2 Duo E4000 and E6000

C3 Deep Sleep Pentium II and above, but not on Core 2 Duo E4000 and E6000; Turion 64

C3 AltVID AMD Turion 64

C4 Deeper Sleep Pentium M and above, but not on Core 2 Duo E4000 and E6000 series; AMD Turion 64

C4E/C5 Enhanced Deeper Sleep Core Solo, Core Duo and 45-nm mobile Core 2 Duo only

C6 Deep Power Down 45-nm mobile Core 2 Duo only

この表 (一部のケースでは間違っていることが後でわかりました) から、Core 2 プロセッサでは C ステートのサポートにさまざまな違いがあったことがわかります (Core を除いて、ほぼすべての Core 2 プロセッサはソケット LGA775 であることに注意してください)。 2 Solo SU3500 (Socket BGA956 および Merom/Penryn プロセッサ)。「Intel Core」Solo/Duo プロセッサは、Socket PBGA479 または PPGA478 のいずれかです。

表の追加の例外は、この記事で見つかりました:

<ブロック引用>Intel の Core 2 Duo E8500 は C-state C2 および C4 をサポートしていますが、Core 2Extreme QX9650 はサポートしていません。

興味深いことに、QX9650 は Yorkfield プロセッサ (Intel ファミリ 6、モデル 23、ステッピング 6) です。参考までに、私の Q9550S は Intel ファミリ 6、モデル 23 (0x17)、ステッピング 10 で、C-state C4 をサポートしていると思われます (実験で確認済み)。さらに、Core 2 Solo U3500 は Q9550S と同じ CPUID (ファミリ、モデル、ステッピング) を持っていますが、LGA775 以外のソケットで利用できるため、上の表の解釈が混乱します。

明らかに、CPUID は、このプロセッサ モデルの C ステート サポートを識別するために、少なくともステッピングまで使用する必要があり、場合によっては不十分な場合があります (現時点では未定)。

CPU アイドル情報を割り当てるためのメソッド シグネチャは次のとおりです:

#define ICPU(model, cpu) \

{ X86_VENDOR_INTEL, 6, model, X86_FEATURE_ANY, (unsigned long)&cpu }

どこで 58 asm/intel-family.h に列挙されています。このヘッダー ファイルを調べると、Intel CPU には、Intel ファミリ 6 のモデル番号と一致するように見える 8 ビットの識別子が割り当てられていることがわかります:

#define INTEL_FAM6_CORE2_PENRYN 0x17

上記から、インテル ファミリ 6、モデル 23 (0x17) は 62 として定義されています。 .ほとんどのモデル 23 プロセッサのアイドル状態を定義するにはこれで十分ですが、上記のように QX9650 で問題が発生する可能性があります。

したがって、最低限、個別の C ステート セットを持つプロセッサの各グループをこのリストで定義する必要があります。

Zagacki と Ponnala、インテル テクノロジー ジャーナル 12 (3):219-227, 2008 は、Yorkfield プロセッサが実際に C2 と C4 をサポートしていることを示しています。また、ACPI 3.0a 仕様が C0、C1、C2、および C3 間の遷移のみをサポートしていることも示しているようです。 限定された一連の C ステート間を遷移するドライバー。ただし、この記事では、必ずしもそうとは限らないことを示しています:

<ブロック引用>これはプロセッサの状態ではなく ACPI C の状態であるため、ACPIC3 は HW C6 などになる可能性があることに注意してください。

また、注意:

<ブロック引用>プロセッサ自体を超えて、C4 はプラットフォーム内の主要なシリコン コンポーネント間の同期作業であるため、Intel Q45 ExpressChipset は 28% の電力向上を実現します。

私が使用しているチップセットは確かに Intel Q45 Express チップセットです。

MWAIT に関する Intel のドキュメントは簡潔ですが、BIOS 固有の ACPI 動作を確認しています:

<ブロック引用>MWAIT 拡張で定義されたプロセッサ固有の C ステートは、ACPI で定義された C ステート タイプ (C0、C1、C2、C3) にマップできます。マッピング関係は、プロセッサの実装による C ステートの定義に依存し、ACPI 定義の _CST テーブルを使用して BIOS によって OSPM に公開されます。

上記の表の私の解釈 (ウィキペディア、asm/intel-family.h、および上記の記事の表と組み合わせたもの) は次のとおりです。

モデル 9 0x09 (Pentium M およびCeleron M ):

- バニアス:C0、C1、C2、C3、C4

モデル 13 0x0D (Pentium M およびCeleron M ):

- ドーサン、スティーリー:C0、C1、C2、C3、C4

モデル 14 0x0E INTEL_FAM6_CORE_YONAH (拡張 Pentium M 、強化された Celeron M または Intel Core ):

- ヨナ (コア ソロ 、コア デュオ ):C0、C1、C2、C3、C4、C4E/C5

モデル 15 0x0F INTEL_FAM6_CORE2_MEROM (いくつかの Core 2 および Pentium デュアルコア ):

- ケンツフィールド、メロム、コンロー、アレンデール (E2xxx/E4xxx および Core 2 Duo E6xxx、T7xxxx/T8xxxx 、コア 2 エクストリーム QX6xxx 、コア 2 クワッド Q6xxx ):C0、C1、C1E、C2、C2E

モデル 23 0x17 INTEL_FAM6_CORE2_PENRYN (コア 2 ):

- Merom-L/Penryn-L:?

- Penryn (Core 2 Duo 45 nm モバイル ):C0、C1、C1E、C2、C2E、C3、C4、C4E/C5、C6

- Yorkfield (コア 2 エクストリーム QX9650 ):C0、C1、C1E、C2E?、C3

- ウルフデール/ヨークフィールド (コア 2 クワッド 、C2Q Xeon 、コア 2 デュオ E5xxx/E7xxx/E8xxx 、Pentium デュアルコア E6xxx 、Celeron デュアルコア ):C0、C1、C1E、C2、C2E、C3、C4

プロセッサのコア 2 ラインだけでの C ステート サポートの多様性から、C ステートの一貫したサポートの欠如が、80 運転者。コア 2 ライン全体について、上記のリストを完全に完成させたいと思います。

これらのプロセッサで堅牢な省電力 MWAIT C ステートを十分に活用していないために、どれだけの不要な電力が使用され、過剰な熱が生成されているか (そして現在も生成されているか) を考えると、これは実際には満足のいく答えではありません。

Chattopadhyay 他 2018 年、Energy Efficient High Performance Processors:Recent Approaches for Designing Green High Performance Computing は、Q45 Express チップセットで私が探している特定の動作について注目に値します。

<ブロック引用>パッケージ C ステート (PC0-PC10) - コンピューティング ドメイン、コアおよびグラフィックス (GPU) がアイドル状態の場合、プロセッサには、アンコアおよびプラットフォーム レベルで追加の電力節約の機会があります。たとえば、LLC をフラッシュし、メモリ コントローラーをパワー ゲーティングします。と DRAM IO を備えており、ある状態では、常時オンの電源ドメインでその状態を維持しながら、プロセッサ全体をオフにすることができます。

テストとして、linux/drivers/idle/intel_idle.c の 127 行目に以下を挿入しました:

static struct cpuidle_state conroe_cstates[] = {

{

.name = "C1",

.desc = "MWAIT 0x00",

.flags = MWAIT2flg(0x00),

.exit_latency = 3,

.target_residency = 6,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C1E",

.desc = "MWAIT 0x01",

.flags = MWAIT2flg(0x01),

.exit_latency = 10,

.target_residency = 20,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

// {

// .name = "C2",

// .desc = "MWAIT 0x10",

// .flags = MWAIT2flg(0x10),

// .exit_latency = 20,

// .target_residency = 40,

// .enter = &intel_idle,

// .enter_s2idle = intel_idle_s2idle, },

{

.name = "C2E",

.desc = "MWAIT 0x11",

.flags = MWAIT2flg(0x11),

.exit_latency = 40,

.target_residency = 100,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.enter = NULL }

};

static struct cpuidle_state core2_cstates[] = {

{

.name = "C1",

.desc = "MWAIT 0x00",

.flags = MWAIT2flg(0x00),

.exit_latency = 3,

.target_residency = 6,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C1E",

.desc = "MWAIT 0x01",

.flags = MWAIT2flg(0x01),

.exit_latency = 10,

.target_residency = 20,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C2",

.desc = "MWAIT 0x10",

.flags = MWAIT2flg(0x10),

.exit_latency = 20,

.target_residency = 40,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C2E",

.desc = "MWAIT 0x11",

.flags = MWAIT2flg(0x11),

.exit_latency = 40,

.target_residency = 100,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C3",

.desc = "MWAIT 0x20",

.flags = MWAIT2flg(0x20) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 85,

.target_residency = 200,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C4",

.desc = "MWAIT 0x30",

.flags = MWAIT2flg(0x30) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 100,

.target_residency = 400,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C4E",

.desc = "MWAIT 0x31",

.flags = MWAIT2flg(0x31) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 100,

.target_residency = 400,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C6",

.desc = "MWAIT 0x40",

.flags = MWAIT2flg(0x40) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 200,

.target_residency = 800,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.enter = NULL }

};

95 で 983行目:

static const struct idle_cpu idle_cpu_conroe = {

.state_table = conroe_cstates,

.disable_promotion_to_c1e = false,

};

static const struct idle_cpu idle_cpu_core2 = {

.state_table = core2_cstates,

.disable_promotion_to_c1e = false,

};

102 で 1073行目:

ICPU(INTEL_FAM6_CORE2_MEROM, idle_cpu_conroe),

ICPU(INTEL_FAM6_CORE2_PENRYN, idle_cpu_core2),

PXE ノードをすばやくコンパイルして再起動すると、112 になります。 現在表示されているもの:

[ 0.019845] cpuidle: using governor menu

[ 0.515785] clocksource: acpi_pm: mask: 0xffffff max_cycles: 0xffffff, max_idle_ns: 2085701024 ns

[ 0.543404] intel_idle: MWAIT substates: 0x22220

[ 0.543405] intel_idle: v0.4.1 model 0x17

[ 0.543413] tsc: Marking TSC unstable due to TSC halts in idle states deeper than C2

[ 0.543680] intel_idle: lapic_timer_reliable_states 0x2

そして今、PowerTOP は以下を表示しています:

Package | CPU 0

POLL 2.5% | POLL 0.0% 0.0 ms

C1E 2.9% | C1E 5.0% 22.4 ms

C2 0.4% | C2 0.2% 0.2 ms

C3 2.1% | C3 1.9% 0.5 ms

C4E 89.9% | C4E 92.6% 66.5 ms

| CPU 1

| POLL 10.0% 400.8 ms

| C1E 5.1% 6.4 ms

| C2 0.3% 0.1 ms

| C3 1.4% 0.6 ms

| C4E 76.8% 73.6 ms

| CPU 2

| POLL 0.0% 0.2 ms

| C1E 1.1% 3.7 ms

| C2 0.2% 0.2 ms

| C3 3.9% 1.3 ms

| C4E 93.1% 26.4 ms

| CPU 3

| POLL 0.0% 0.7 ms

| C1E 0.3% 0.3 ms

| C2 1.1% 0.4 ms

| C3 1.1% 0.5 ms

| C4E 97.0% 45.2 ms

ついに Enhanced Core 2 C-states にアクセスしました。消費電力が測定可能なほど低下しているように見えます。8 ノードのメーターでは、平均して少なくとも 5% 低下しているようです (1 つのノードがまだ古いカーネルを実行している状態で)。ですが、テストとしてもう一度カーネルを交換してみます。

C4E サポートに関する興味深いメモ - 上記で証明されているように、私の Yorktown Q9550S プロセッサはそれ (または C4 の他のサブステート) をサポートしているようです! Core 2 Q9000 プロセッサの Intel データシート (セクション 6.2) には C ステートのノーマル (C0)、HALT (C1 =0x00)、拡張 HALT (C1E =0x01)、ストップ グラント (C2 =0x10) しか記載されていないため、これは私を混乱させます。 、拡張ストップ グラント (C2E =0x11)、スリープ/ディープ スリープ (C3 =0x20)、ディープ スリープ (C4 =0x30)。この追加の 0x31 状態は何ですか?状態 C2 を有効にすると、C4 の代わりに C4E が使用されます。状態 C2 を無効にする (状態 C2E を強制する) と、C4E の代わりに C4 が使用されます。これは MWAIT フラグと関係があると思われますが、この動作に関するドキュメントはまだ見つかりません.

C1E 状態は C1 の代わりに使用され、C2 は C2E の代わりに使用され、C4E は C4 の代わりに使用されているようです。 C1/C1E、C2/C2E、および C4/C4E を 121 と一緒に使用できるかどうかはわかりません またはそれらが冗長である場合。 Intel Labs Pittsburgh によるこの 2010 年のプレゼンテーションで、トランジションが C0 - C1 - C0 - C1E - C0 であり、さらに次のように述べているメモを見つけました:

C1E は、すべてのコアが C1E にある場合にのみ使用されます

これは、すべてのコアが C1E 状態にある場合にのみ、他のコンポーネント (メモリなど) で C1E 状態になると解釈されると考えています。私はこれを C2/C2E および C4/C4E 状態にも同等に適用すると考えています (ただし、C4E は「C4E/C5」と呼ばれているため、C4E が C4 のサブ状態なのか、C5 がサブ状態なのかはわかりません。 C4E の状態。テストでは、C4/C4E が正しいことが示されているようです)。 C2 状態をコメントアウトすることで C2E を強制的に使用できますが、これにより C4E の代わりに C4 状態が使用されます (ここではさらに作業が必要になる場合があります)。モデル 15 またはモデル 23 のプロセッサで C2E 状態を欠いているものがないことを願っています。これらのプロセッサは、上記のコードでは C1/C1E に限定されるためです。

また、フラグ、レイテンシ、レジデンシーの値はおそらく微調整される可能性がありますが、Nehalem のアイドル値に基づいて知識に基づいた推測を行うだけでも問題ないようです。改善するには、さらに読む必要があります。

Core 2 Duo E2220 (Allendale)、Dual Core Pentium E5300 (Wolfdale)、Core 2 Duo E7400、Core 2 Duo E8400 (Wolfdale)、Core 2 Quad Q9550S (Yorkfield)、および Core 2 Extreme QX9650 でこれをテストしました。状態 C2/C2E および C4/C4E に対する前述の優先事項を超える問題は見つかりませんでした。

このドライバーの変更の対象外:

- 元の Core Solo/Core Duo (Yonah、Core 2 以外) はファミリ 6、モデル 14 です。これは、C4E/C5 (Enhanced Deep Sleep) C ステートをサポートしていたが、C1E/C2E ステートをサポートしていなかったため、良好です。独自のアイドル定義が必要になります。

考えられる唯一の問題は次のとおりです。

- Core 2 Solo SU3300/SU3500 (Penryn-L) はファミリ 6、モデル 23 であり、このドライバによって検出されます。ただし、ソケット LGA775 ではないため、C1E Enhanced Halt C-state をサポートしていない可能性があります。 Core 2 Solo ULV U2100/U2200 (Merom-L) についても同様です。ただし、

134ドライバーは、サブステートのハードウェア サポートに基づいて、適切な C1/C1E を選択するようです。 - Core 2 Extreme QX9650 (Yorkfield) は、C-state C2 または C4 をサポートしていないと報告されています。これは、中古の Optiplex 780 および QX9650 Extreme プロセッサを eBay で購入して確認しました。プロセッサは、C ステート C1 および C1E をサポートします。このドライバーの変更により、CPU は C1 ではなく C1E 状態でアイドル状態になるため、おそらく電力がいくらか節約されます。 C-state C3 が表示されることを期待していましたが、このドライバーを使用すると表示されないため、さらに調査する必要があるかもしれません。

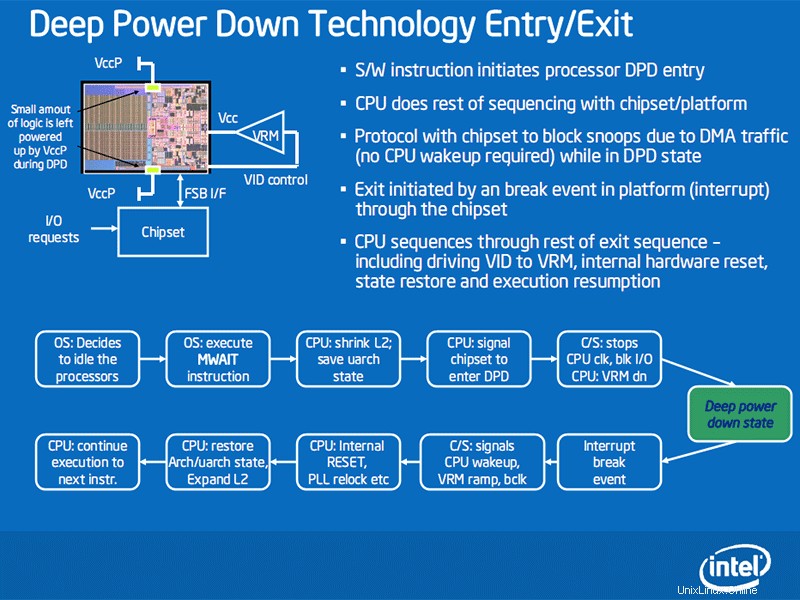

2009 年の Intel プレゼンテーションから、C ステート間の遷移 (つまり、ディープ パワー ダウン) に関するスライドを見つけることができました:

結論として、144 で Core 2 がサポートされていなかった本当の理由はなかったことが判明しました。 運転者。 「Core 2 Duo」の元のスタブ コードが C ステート C1 と C2 のみを処理したことは明らかであり、これは 158 よりもはるかに効率が悪い C ステート C3 も処理する関数。どこを見ればよいかがわかれば、サポートの実装は簡単でした。有益なコメントやその他の回答は非常に高く評価されました。Amazon が耳を傾けているのであれば、小切手の送り先がわかります。

この更新は github にコミットされています。 LKML へのパッチをすぐに電子メールで送信します。

更新 :また、ファミリー 6、モデル 15 である Socket T/LGA775 Allendale (Conroe) Core 2 Duo E2220 を掘り出すことができたので、そのサポートも追加しました。このモデルは C-state C4 をサポートしていませんが、C1/C1E および C2/C2E をサポートしています。これは、他の Conroe ベースのチップ (E4xxx/E6xxx) や、おそらくすべての Kentsfield および Merom (非 Merom-L) プロセッサでも機能するはずです。

更新 :ようやく MWAIT チューニング リソースを見つけました。この Power vs. Performance の記事と、この Deeper C の状態とレイテンシの増加に関するブログ投稿の両方に、CPU のアイドル レイテンシを特定するための有用な情報が含まれています。残念ながら、これはカーネルにコード化された終了レイテンシのみを報告します (ただし、興味深いことに、プロセッサがサポートするハードウェア状態のみを報告します):

# cd /sys/devices/system/cpu/cpu0/cpuidle

# for state in `ls -d state*` ; do echo c-$state `cat $state/name` `cat $state/latency` ; done

c-state0/ POLL 0

c-state1/ C1 3

c-state2/ C1E 10

c-state3/ C2 20

c-state4/ C2E 40

c-state5/ C3 20

c-state6/ C4 60

c-state7/ C4E 100

更新: インテルの従業員が最近 162 に関する記事を公開しました MWAIT 状態の詳細。

<ブロック引用>

このプロセッサ ファミリの最適な CPU アイドル サポートのためにカーネルを構成するより適切な方法はありますか (intel_idle のサポートを無効にする以外に)

ACPI が有効になっており、acpi_idle が使用されていることを確認しました。役立つカーネル構成オプションを見落としていないことを心から疑います。 177 はいつでも確認できます 可能性のある提案についてですが、おそらくすでにそれを知っていたでしょう.

これは答えではありませんが、フォーマットしたいと思います:-(.

<ブロック引用>カーネル ソース コードを見ると、現在の intel_idle ドライバーには、インテル ファミリー 6 をドライバーから明確に除外するためのテストが含まれています。

いいえ、そうではありません:-)。

id = x86_match_cpu(intel_idle_ids);

if (!id) {

if (boot_cpu_data.x86_vendor == X86_VENDOR_INTEL &&

boot_cpu_data.x86 == 6)

pr_debug(PREFIX "does not run on family %d model %d\n",

boot_cpu_data.x86, boot_cpu_data.x86_model);

return -ENODEV;

}

188 このステートメントはファミリー 6 を除外していません。代わりに、197 ステートメントは、デバッグが有効になっているときに、この特定の最新の Intel CPU が 200 でサポートされていないというメッセージを提供します .実際、私の現在の i5-5300U CPU はファミリー 6 で、210 を使用しています。 .

あなたのCPUを除外するのは、223に一致がないことです

テーブルを実装したこのコミットに気付きました。削除するコードには 237 がありました 代わりにステートメント。これにより、最も初期のモデル intel_idle が実装されている/テストに成功した/0x1A =26 であることを簡単に確認できます。

これは、機会とコストの問題にすぎないと思います。 247のとき Core 2 Duo のサポートが計画されていたようですが、完全には実装されていませんでした。式は比較的複雑です:259 261 よりも十分なメリットを提供する必要があります 十分な数の「改善された」カーネルが見られる CPU で、ここでサポートする価値があるようにするために...

sourcejedi の回答が示すように、ドライバーはファミリー 6 のすべてを除外するわけではありません。270 Nehalem から Kaby Lake まで、基本的にすべてのマイクロアーキテクチャをカバーする、CPU モデルのリスト内の CPU の初期化チェック。 Yorkfield はそれよりも古い (そして大きく異なる — Nehalem はそれ以前のアーキテクチャとは大きく異なっている)。ファミリ 6 テストは、エラー メッセージが出力されるかどうかのみに影響します。その影響は、AMD CPU ではなく、Intel CPU でのみエラー メッセージが表示されることだけです (Intel ファミリ 6 には、Pentium Pro 以降のすべての非 NetBurst Intel CPU が含まれます)。

構成に関する質問に答えるには、286 を完全に無効にすることができます 、しかし、そのままにしておいても問題ありません (警告が気にならない限り)。